Geany windows(集成开发环境) 1.34

下载

phpstudy(php集成开发环境) 8.1.0.1

下载

codeblocks (C/C++ 集成开发环境) 13.12.1

下载

Komodo Edit(多语言集成开发环境) 11.0.0

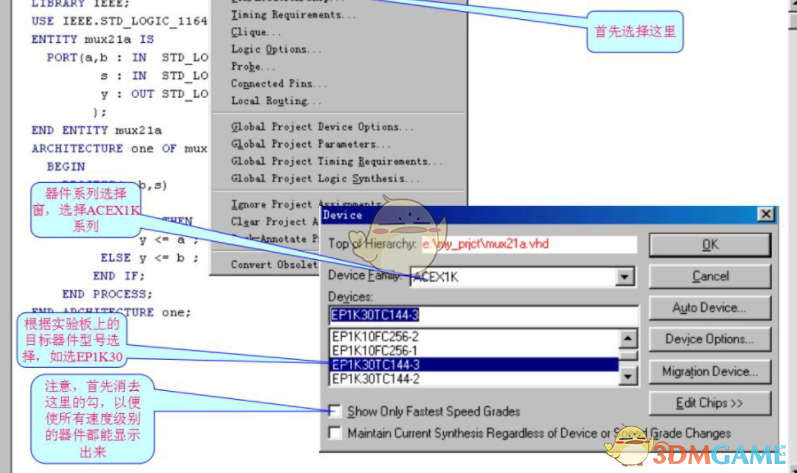

下载《maxplusii软件 10.2》是一款PLD开发系统;这款软件给用户提供了FPGA、CPLD集成开发环境,还支持完成您需要的设计输入,仿真、元件适配等功能,软件内的功能非常丰富,操作也很简单,是一款非常不错的软件,感兴趣的小伙伴欢迎下载使用噢!

是业界最优秀的混合HDL语言仿真调试环境,提供最佳的仿真性能和调试特征,成为众多ASIC和FPGA厂商推荐的仿真调试工具,也是广大FPGA、ASIC设计工程师实施混合HDL语言RTL级、门级电路仿真以及布局布线后时序仿真的首选。全面支持所有HDL标准,支持广泛的建模技术,提供直观的图形用户界面运行方式,也支持高性能的批处理模式。

单内核支持混合HDL的仿真与调试。

编译仿真速度快。编译代码与机器和软件版本无关,设计的移植以及库的维护非常简便。

支持加密方式的IP,实现对IP核的保护。

集成的C调试环境,在统一的界面中可以同时仿真调试C 和混合HDL设计。

Signal Spy功能可以方便地访问混合HDL设计中的内部信号方便设计的调试。

先进的数据流窗口,可以迅速追踪并且定位导致不定状态的原因,显示全部可能的路径。

性能分析工具帮助分析仿真的性能瓶颈,加速设计仿真。

波形窗口可以显示多组波形,并且进行多种模式的波形比较。

先进的代码覆盖率检查模块可以报告HDL语句和分支的执行情况,确保测试的完整性。

提供源代码模版和助手功能。

1.设计输入。在传统设计中,设计人员是应用传统的原理图输入方法来开始设计的。自90年代初, Verilog、VHDL、AHDL等硬件描述语言的输入方法在大规模设计中得到了广泛应用。

2.前仿真(功能仿真)。设计的电路必须在布局布线前验证电路功能是否有效。(ASCI设计中,这一步骤称为第一次Sign-off)PLD设计中,有时跳过这一步。

3.设计编译。设计输入之后就有一个从高层次系统行为设计向门级逻辑电路设转化翻译过程,即把设计输入的某种或某几种数据格式(网表)转化为软件可识别的某种数据格式(网表)。

4.优化。对于上述综合生成的网表,根据布尔方程功能等效的原则,用更小更快的综合结果代替一些复杂的单元,并与指定的库映射生成新的网表,这是减小电路规模的一条必由之路。

5.布局布线。在PLD设计中,3-5步可以用PLD厂家提供的开发软件(如 Maxplus2)自动一次完成。

6.后仿真(时序仿真)需要利用在布局布线中获得的精确参数再次验证电路的时序。(ASCI设计中,这一步骤称为第二次Sign—off)。

7.生产。布线和后仿真完成之后,就可以开始ASCI或PLD芯片的投产

quartusii和maxplusii的区别

QuartusII 和 MAX+PLUS II 都是 Altera 公司出品的开发FPGA的工具,早期开发者一般用MAX+PLUS II,MAX最高版本好像是10.0,后来就出品QuartusII了,故可以吧QuartusII 看做MAX的升级。目前QuartusII 最高版本已经到8.0了。但好像破解这个版本的Crack还没有。

一般第一次运行QuartusII的时候,QuartusII都会弹出对话框,问你使用MAX+PLUSII风格的界面还是QuartusII的界面,如果您以前没用过MAX,建议直接用QuartusII的风格。

另外,现在好像已经没多少人用MAX+PLUS II了,所以直接用QuartusII开发FPGA就可以了。

Geany windows(集成开发环境) 1.34

下载

phpstudy(php集成开发环境) 8.1.0.1

下载

codeblocks (C/C++ 集成开发环境) 13.12.1

下载

Komodo Edit(多语言集成开发环境) 11.0.0

下载

印象笔记在线版

下载

Kazumi动漫

下载

EV扩展屏电脑版

下载

极客编辑器1.0.12

下载24.51MB

2025-09-30

18.92MB

2025-09-30

80.15MB

2025-09-30

26.64MB

2025-09-30

124.48MB

2025-09-30

18.56MB

2025-09-30

84.55MB / 2025-09-30

248.80MB / 2025-07-09

2.79MB / 2025-08-22

63.90MB / 2025-07-08

1.90MB / 2025-09-07

210.99MB / 2025-06-09

374.16MB / 2025-01-24

京ICP备14006952号-1 京B2-20201630 京网文(2019)3652-335号 沪公网安备 31011202006753号违法和不良信息举报/未成年人举报:legal@3dmgame.com

CopyRight©2003-2018 违法和不良信息举报(021-54473036) All Right Reserved

玩家点评 (0人参与,0条评论)

热门评论

全部评论